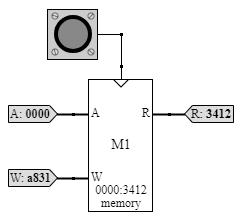

The Memory component implements a simple 16-bit Memory Bank. Memory is an array of bytes. The A (address) input selects a memory location that is output on the R output. The component implements 16-bit memory, so all accesses are considered to be multiples of two and retrieve two bytes. Memory is retrieved in little-endian mode (first byte is the least significant byte).

A clock cycle on the clock input writes the memory component with the value on the W (write) input. The value on W is written to memory on the rising clock edge.

Memory can be specified in the component dialog box as a sequence of Hexadecimal byte values:

12 34 a8 93 b7 00 12 9a

Spaces and new-lines are ignored. Addresses can optionally be included at the beginning of lines:

0000: 12 34 a8 93 b7 00 12 9a 0008: 18 b7

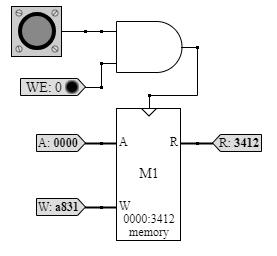

The clock input will always write memory when cycles to true and back to false. The memory component does not have a write enable input. However, it is easy to make one by using an AND gate: